摘要:本文主要研究同步时序逻辑电路设计,探讨其设计原理、方法和应用。通过对同步时序逻辑电路的特点进行深入分析,研究其在不同领域的应用及其性能表现。本文旨在提高同步时序逻辑电路设计的可靠性和效率,为相关领域的发展提供支持。

随着信息技术的飞速进步,数字电路设计的复杂性不断提升,对时序逻辑电路的设计要求也越来越高,同步时序逻辑电路作为数字电路的核心组成部分,其设计质量直接关系到整个系统的性能与稳定性,本文将深入探讨同步时序逻辑电路设计的基本原理、方法、流程以及关键注意事项。

同步时序逻辑电路概述

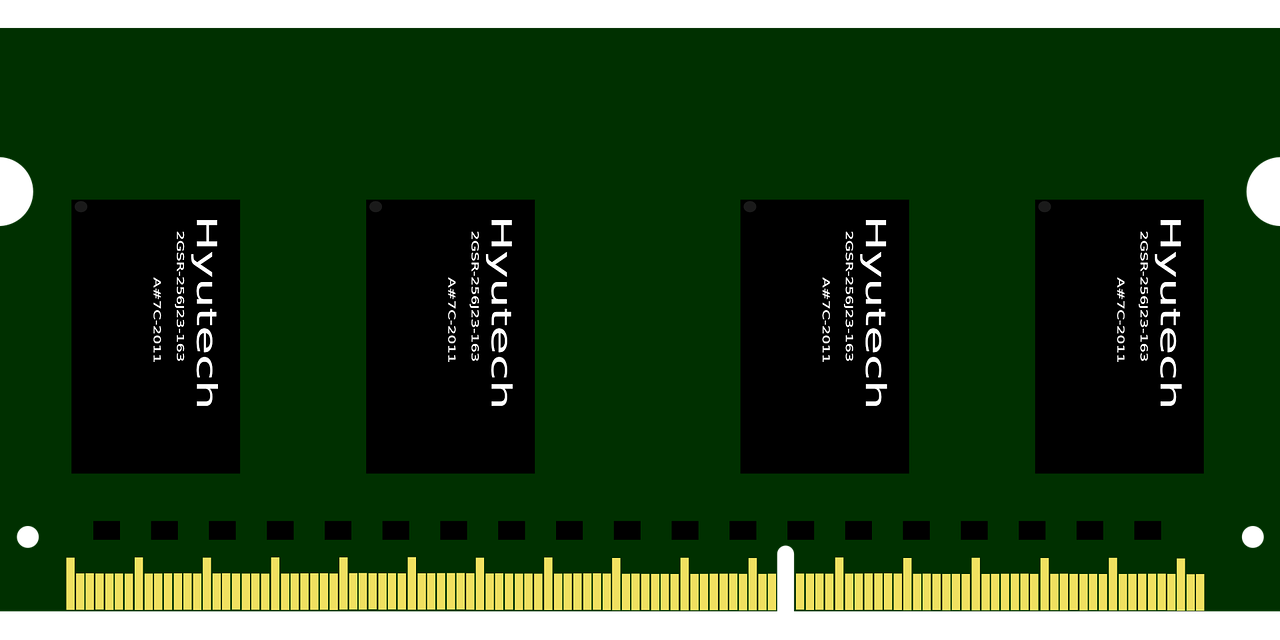

同步时序逻辑电路是一种基于时钟信号驱动的数字电路,其输出状态仅由当前时刻的输入状态和时钟信号决定,具有确定性强、易于设计与分析等优点,广泛应用于计算机、通信、控制等领域。

同步时序逻辑电路设计原理

同步时序逻辑电路的设计主要依据数据流程图和状态转换表,设计时需明确系统的输入和输出,然后构建状态转换逻辑,实现系统状态的转移,设计过程中,需充分考虑时钟信号的频率、稳定性以及延迟等因素对电路性能的影响,遵循以下设计原则:

1、简洁性:设计应尽可能简洁,避免不必要的复杂性和冗余。

2、可靠性:设计应具有高可靠性,确保在恶劣环境下仍能正常工作。

3、高效性:设计应具有高效性,能在规定的时间内完成预期的功能。

同步时序逻辑电路设计流程

同步时序逻辑电路的设计流程主要包括以下步骤:

1、确定设计目标:明确设计需求,确定系统的输入和输出。

2、设计状态转换表:根据实际需求,制定详细的状态转换表,明确系统在不同状态下的行为。

3、器件选择:根据设计需求,精心选择逻辑器件,如触发器、门电路等。

4、逻辑图绘制:根据设计原理和状态转换表,绘制逻辑图,实现电路的连接。

5、仿真验证:通过仿真软件对设计进行验证,确保设计的正确性和可靠性。

6、布局布线:根据实际需求进行布局布线,确保电路的性能和稳定性。

7、测试与优化:对实际电路进行测试,根据测试结果进行优化,进一步提升电路性能。

同步时序逻辑电路设计注意事项

1、时钟信号的选择:时钟信号的频率和稳定性对同步时序逻辑电路的性能具有重要影响,设计时需充分考量。

2、延迟时间的影响:同步时序逻辑电路中的延迟时间会影响系统的实时性,设计过程中需充分考虑并优化。

3、避免竞争与冒险现象:在同步时序逻辑电路中,需采取措施避免竞争与冒险现象的发生,以确保电路的稳定性和可靠性。

4、冗余设计:为提高电路的可靠性,可适当添加冗余设计,如增加备用触发器等。

5、可测试性:设计时需考虑电路的测试性,以便于在实际应用中进行维护与调试。

6、其他注意事项:设计者还需关注电源噪声、电磁干扰等因素对同步时序逻辑电路设计的影响,确保设计的鲁棒性,不断学习和掌握最新的设计工具和技术,提高设计效率和质量,同步时序逻辑电路设计是数字电路设计的重要组成部分,其设计质量直接关系到整个系统的性能和稳定性,本文提供的参考依据和设计建议,旨在为设计者在实际设计中提供指导和帮助。

陕ICP备19005503号-2

陕ICP备19005503号-2

还没有评论,来说两句吧...