摘要:本文介绍了数字时钟电路的设计过程。该设计涉及使用适当的电子元件和集成电路来创建一个能够准确显示时间的数字时钟。设计过程包括选择适当的时钟芯片、电源管理模块、显示模块等,并进行电路布局和连接。该数字时钟电路能够提供精确的时间信息,适用于各种应用场景。

数字时钟电路设计的基本原理

数字时钟电路的核心是利用振荡器产生的稳定时钟信号,通过分频器、计数器、译码器等电路模块,实现时间的精确计数和显示,设计过程中,需重点考虑时钟信号的稳定性、功耗、集成度等因素。

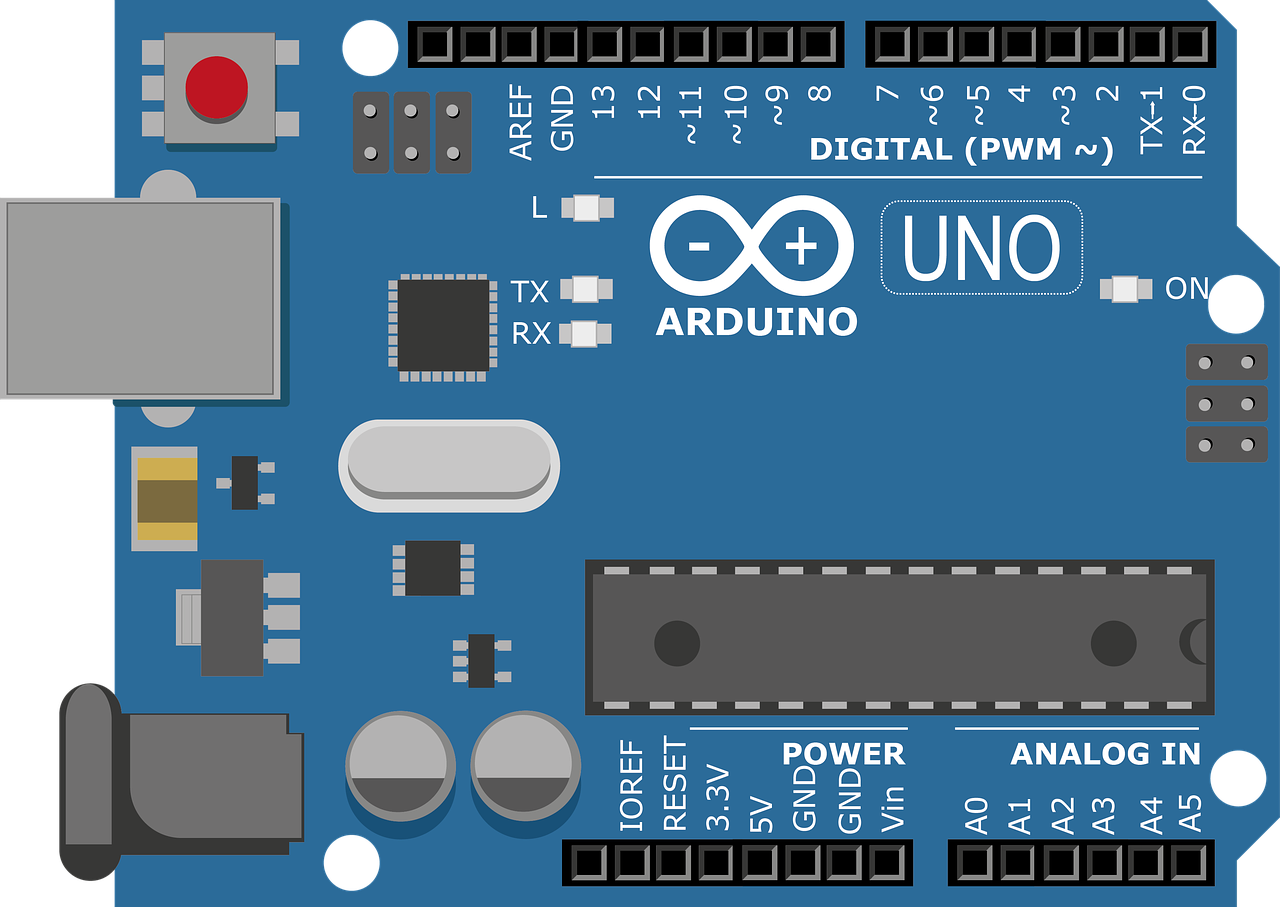

主要元器件选择

1、时钟振荡器:作为时钟电路的核心,负责产生稳定的时钟信号,\n2. 分频器:对时钟信号进行分频,产生计数的脉冲信号,\n3. 计数器:对脉冲信号进行计数,实现时间的精确计数功能,\n4. 译码器:将计数器的输出转换为七段显示器的驱动信号,实现时间显示,\n5. 七段显示器:用于时间的显示,是电路的输出设备。

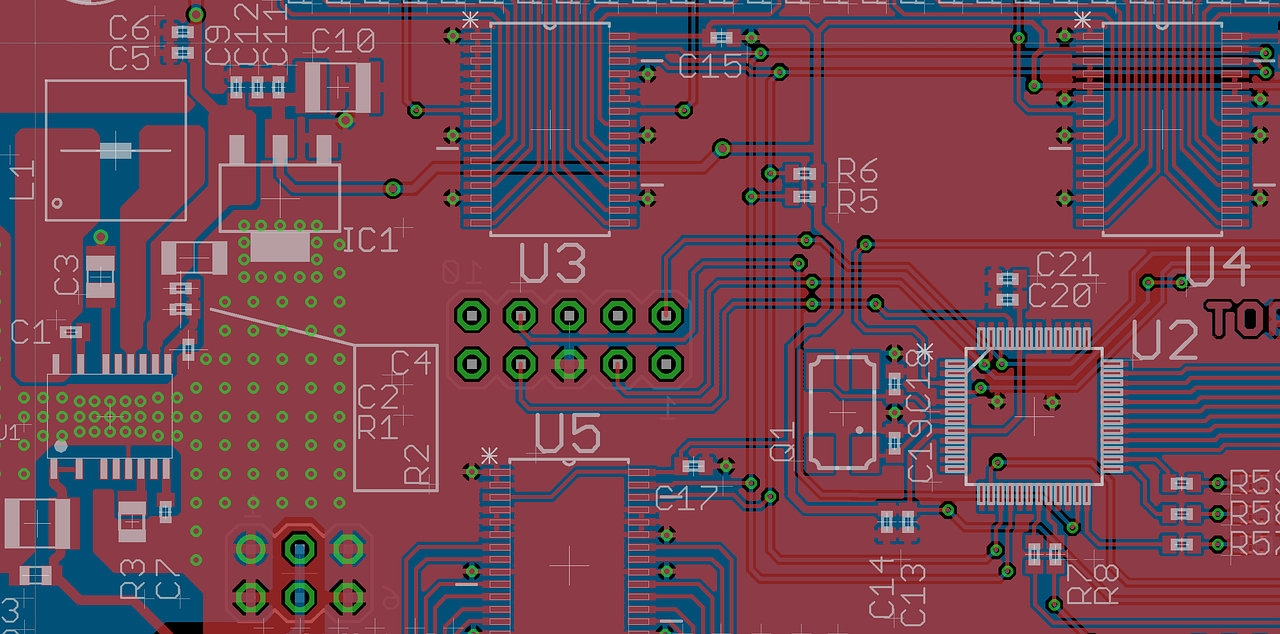

电路设计步骤

1、设计时钟信号产生电路:选择稳定的振荡器,考虑频率稳定性和温度特性,\n2. 设计分频器电路:根据需求选择合适的分频器,考虑计数精度和功耗,\n3. 设计计数器电路:选择合适的计数器,考虑计数范围和速度,\n4. 设计译码器电路:将计数器输出转换为七段显示器信号,考虑显示清晰度和电路复杂性,\n5. 设计七段显示器接口电路:连接译码器与显示器,考虑驱动方式和接口类型,\n6. 总体布局与布线:根据原理图和元器件特性,进行合理布局和布线,注重信号质量和抗干扰性,\n7. 电源设计:提供稳定电源供应,考虑电压、电流和稳定性。

电路调试与优化

1、调试前准备:检查电路连接和元器件参数,\n2. 调试过程:测试时钟信号、分频器、计数器和译码器等电路,验证功能正常,\n3. 问题排查:如发现问题,从电源、时钟信号、电路输出等方面入手,逐步定位问题,\n4. 电路优化:根据调试结果进行优化,提高性能和稳定性,优化措施包括改进元器件、优化布局布线、调整电路参数等。

数字时钟电路设计是一个综合性的过程,需要综合考虑时钟信号的稳定性、功耗和集成度等因素,通过合理的设计、元器件选择、调试与优化,可以实现数字时钟电路的精确控制和时间显示,本文提供的详细介绍为数字时钟电路的设计提供了有益的参考,在实际应用中,还需根据具体需求和条件进行灵活调整和创新。

转载请注明来自扩散硅压力传感器_单晶硅压力变送器_电磁流量计厂家-陕西联航科技有限公司,本文标题:《数字时钟电路设计详解》

陕ICP备19005503号-2

陕ICP备19005503号-2

还没有评论,来说两句吧...