摘要:,,本文探讨了芯片ESD(静电放电)防护机制的重要性与应用前景。随着电子设备的广泛应用,芯片ESD问题日益突出,对电子设备的安全与可靠性构成严重威胁。深入研究芯片ESD防护机制,提高芯片的抗静电能力,对于保障电子设备正常运行至关重要。本文还介绍了ESD防护机制的应用前景,指出其在未来电子产业发展中的重要作用。

芯片ESD现象及其影响

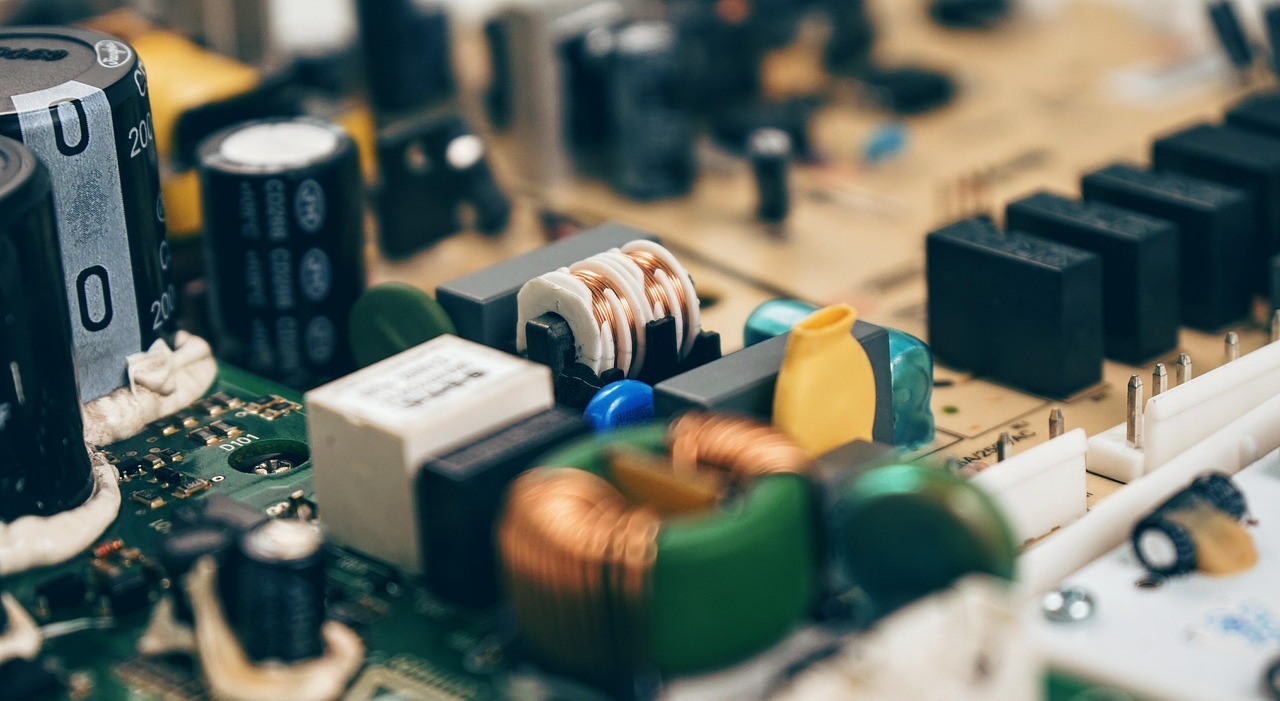

静电放电(ESD)是指静电电荷的突然释放,其电压和电流峰值非常高,在芯片制造、运输、使用等环节,ESD事件可能导致芯片表面电荷积累,进而引发静电击穿,对芯片造成永久性损坏,ESD还可能引起芯片内部电路瞬态干扰,导致功能失效或性能下降。

芯片ESD防护机制的重要性

芯片ESD防护机制在保护芯片免受静电放电损害方面具有重要意义,在芯片制造的全过程,从电路设计、封装与组装到材料选择,ESD防护都扮演着至关重要的角色,在制造环节,有效的ESD防护措施有助于减少芯片在生产过程中的损坏率,提高生产效率和产品质量,在运输和存储环节,ESD防护能确保芯片在恶劣环境下的安全性,避免静电放电导致的损坏,在使用环节,良好的ESD防护机制能延长芯片的使用寿命,提高电子产品的可靠性和稳定性。

芯片ESD防护机制的应用

1、电路设计阶段的ESD防护:在芯片设计初期,应充分考虑ESD防护需求,采用具有ESD保护功能的电路结构,如采用钳位二极管和瞬态抑制器等元件,将ESD电流引入地线,从而保护芯片。

2、封装与组装阶段的ESD防护:采用导电性良好的包装材料,确保芯片与包装材料之间的良好接触,以释放积累的静电电荷。

3、材料选择阶段的ESD防护:选择具有优异导电性和抗静电性的材料,降低芯片在制造、运输和使用过程中的静电积累,采用抗静电涂层技术,提高芯片的抗静电能力。

4、系统层面的ESD防护:在电子产品系统中,采取整体ESD防护措施,如设置防静电地线、使用防静电工作台面等,为芯片提供一个良好的静电防护环境。

芯片ESD防护机制的应用前景

随着物联网、人工智能、5G通信等技术的快速发展,集成电路的集成度越来越高,芯片的复杂度也随之增加,这将使得ESD问题更加严重,对芯片ESD防护机制的研究与应用提出了更高的要求,随着新材料、新工艺、新技术的不断发展,芯片ESD防护机制将不断完善和创新,为电子产品的性能提升和稳定性保障提供有力支持,芯片ESD防护机制将更加注重智能化、高效化和集成化,以满足不断发展的科技需求。

芯片ESD防护机制对于保护芯片免受静电放电损害具有重要意义,随着科技的发展,芯片ESD防护机制的研究与应用前景愈发广阔,通过电路设计、封装与组装、材料选择以及系统层面的ESD防护措施,可以有效提高芯片的抗静电能力,确保电子产品的性能与稳定性。

陕ICP备19005503号-2

陕ICP备19005503号-2

还没有评论,来说两句吧...